DekatronPC: различия между версиями

Radiolok (обсуждение | вклад) |

Radiolok (обсуждение | вклад) |

||

| Строка 1: | Строка 1: | ||

| Строка 421: | Строка 423: | ||

!Тест | !Тест | ||

!Состояние | !Состояние | ||

|- | |||

|Dekatron | |||

|PASSED | |||

|- | |||

|Counter | |||

|PASSED | |||

|- | |||

|IpLine - LoopTest | |||

|PASSED | |||

|- | |- | ||

|Hello World | |Hello World | ||

Версия 08:01, 22 мая 2023

Описание

Компьютер на базе сверхминиатюрных вакуумных и газоразрядных ламп, процессор которого не содержит кремниевых полупроводниковых элементов.

Ламповый компьютер DekatronPC предназначен для выполнения программ, написанных яна языке программирования brainfuck. Это значит, что основу набора инструкций составляет восемь инструкций языка brainfuck: +-<>.,[]

Основное требование к ламповому компьютеру — чтобы инструкции в нем в точности соответствовали языку Brainfuck. Во-вторых — 99% существующих восьмибитных программ на Brainfuck должны исполняться исключительно на ламповой логике. Оставшийся 1% банально может не умещаться в ОЗУ. Максимум того, что допускается использовать в аутентичной части машины, — это германиевые диоды, да и то лишь в выпрямителях питания в схемах обвязки кубов памяти.

Подпроекты

- Ламповая логика - Проектирование быстродействующих ламповых логических элементов

- Испытатель электронных ламп - Проект современного портативного испытателя вакуумных и газоразряных ламп

- DekatronPC эмулятор - Verilog-модель лампового компьютера на ПЛИС

Технические характеристики (проектные) - UPD: 19.05.2023

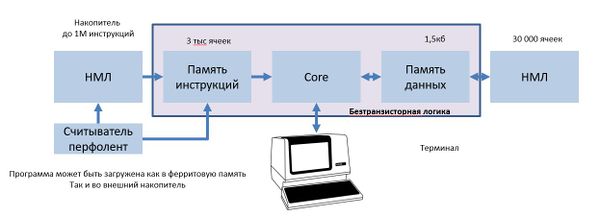

- Архитектура - с раздельной памятью данных и кода.

- Объем памяти программ - 1МиБ, из них:

- Ферритовая память - 1.5киБ

- Внешняя память - до 1МиБ

- Объем памяти данных - 29.29КиБ(30000ячеек данных). из них:

- Ферритовая память - 1 Киб

- Внешняя память (накопитель на магнитной ленте) - до 29.29КиБ

- Разрядность:

- Шины данных - 10 бит октетами в формате 8-4-2-1. диапазон счета - 0-255 (3 декатрона)

- Шина адреса данных - 18 бит, октетами в формате 8-4-2-1. диапазон счета - 0-29999 (5 декатронов)

- Шина адреса программ - 24 бит, октетами в формате 8-4-2-1. диапазон счета - 0-999999 (6 декатронов)

- Тактовая частота - не более 1МГц - ограничение со стороны декатрона А110

- Быстродействие - до 500тыс операций в секунду. Доступна конвейризация - пока выполняется текущая инструкция, допускается выборка новой.

- Время выборки новой инструкции, время исполнения инструкции - уникально.

- Выборка новой инструкции - не быстрее 2 тактов. (в текущей версии кода 6)

- Исполнение инструкций - от 1 такта - зависит от предыдущего состояния. В серии команд ++++ первый инкремент займет два такта, второй и последующие - 1 такт, но так как время выборки новой инструкции не менее 2 тактов и может производиться параллельно, то частота инкрементов будет не выше 500 тысяч в секунду на частоте 1МГц.

- Количество ламп ~1000шт (19.05.2023 - по результатам синтеза Verilog-модели 958шт)

- Используемые лампы:

- 6Н16Б - сверхминиатюрный сдвоенный триод для работы в импульсных устройствах.

- 6Ж2Б - сверхминиатюрный пентод для работы в импульсных устройствах. Утверждается, что может работать в режиме с двумя управляющими сетками.

- 6Х7Б - сврехминиатюрный сдвоенный диод.

- А110 - сверхминиатюрный коммутаторный декатрон со скоростью счета до 1млн имп. в секунду.

- Потребляемая мощность, общая - не хуже 5кВт. Для тысячи ламп 6Н16Б рассчет составляет:

- на накал ламп 6.3В 0,4А/лампа (400А) - 2.5кВт

- анодное 150В 5мА/лампа (5А)- 0,75 кВт

- Общие габариты процессора : три 4U серверных блока размерами 920*420*178мм.

- Масса ) 60кг.

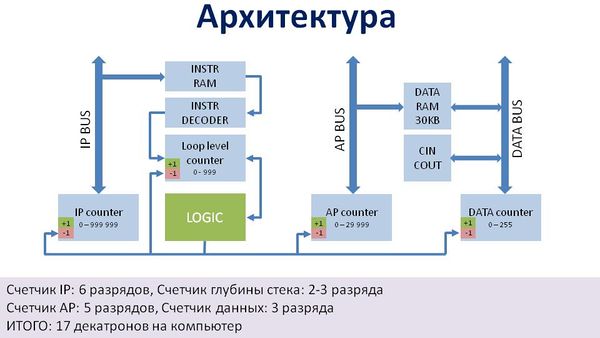

Архитектура

Декатрон — это многоэлектродная газоразрядная лампа, предназначенная для реверсивного счета импульсов. В центре находится диск анода, а вокруг него расположены тридцать электродов. Десяток катодов и две группы подкатодов — по два подкатода между каждым катодом. После подачи напряжения на декатрон между анодом и одним из катодов загорается тлеющий разряд. Подавая импульсы определенной последовательности на подкатоды и соседний катод, мы можем перемещать разряд между катодами, обеспечивая операцию инкремента или декремента. Да эта лампа просто создана для языка Brainfuck!

На базе декатрона мы можем создать простой реверсивный десятичный счетчик. Соединим нужное число таких счетчиков последовательно и получим многоразрядный счетчик, который, например, на базе трех декатронов сможет считать от 0 до 999.

Один такой счетчик на базе шести декатронов будет определять номер текущей исполняемой инструкции. В дополнение к нему нам нужен счетчик глубины вложенности циклов — сумматора в будущем компьютере нет, а значит, начало текущего цикла придется искать вручную, банально перематывая счетчик инструкции назад до тех пор, пока начало нашего цикла не будет найдено. Счетчик вложенных циклов поможет корректно искать нужное начало, даже если внутри нашего цикла множество вложенных. Счетчика от 0 до 999 будет более чем достаточно: в программах на Brainfuck, написанных людьми, даже больше 20–30 уровней вложенности циклов — редкость.

Третий счетчик от 0 до 29 999 будет определять номер текущей ячейки данных. Так как у нас чистый Brainfuck, то и число ячеек в точности соответствует исходной спецификации. Декатронный счетчик можно сбросить при любых значениях.

По адресу этого счетчика происходит выборка данных из ОЗУ. Данные помещаются в четвертый счетчик, который умеет считать от 0 до 255. То есть мы загружаем в декатрон наше старое значение, делаем инкремент или декремент и выгружаем данные обратно в память.

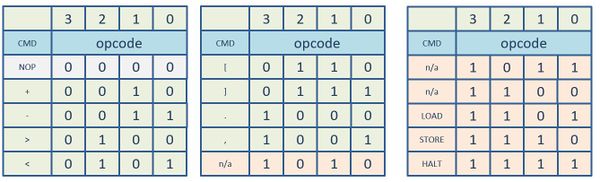

Набор инструкций (Актуальная версия на 18 марта 2022г.)

Общая концепция

В итоге мы имеем:

- NOP — пустая инструкция, необходимая для выравнивания циклов внутри кеш-линеек;

- + и - — инкремент и декремент текущей ячейки данных;

- < и > — изменение номера текущей ячейки;

- [ и ] — начало и конец цикла;

- . и , — печать текущего символа в консоль и ввод из консоли.

Инструкция кодируется четырехбитным значением, а это значит, что остается еще семь свободных инструкций, которые можно использовать для управления машиной.

Например, инструкция HALT остановит машину при завершении работы программы. Еще две инструкции — LOAD и STORE — оптимизируют работу с памятью.

Оптимизация доступа к памяти

Допустим, у нас есть десять инструкций +, идущих подряд. Нам придется десять раз повторить следующий набор действий:

- Прочитать значение текущей ячейки и записать его в декатронный счетчик;

- Выполнить операцию инкремента;

- Записать новое значение текущей ячейки из счетчика в ОЗУ.

По факту мы девять раз просто так будем делать загрузку-выгрузку. Проще перед первым инкрементом один раз сделать явно сделать LOAD из памяти в счетчик, а после последнего явно вызвать STORE обратно из счетчика в ОЗУ. Либо ламповая логика должна понимать, какая инструкция будет идти следом за текущей и выполнять LOAD и STORE неявно, не тратя в дальнейшем время на холостые загрузки-выгрузки.

С одной стороны, неявный LOAD/STORE позволит грузить в компьютер программы, написанные на Brainfuck вообще без модификаций. С другой стороны, усложняется логика выборки инструкции, так как при чтении следующей инструкции необходимо учитывать текущее состояние флагов машины и выполнять дополнительные действия.

В итоге выбрал способ неявного LOAD и STORE. За основу взят принцип data-lock.

- Pагружаем новую инструкцию

- Текущая инструкция +(или -).

- Проверяем флаг APLock:

- Флаг снят. значит в счетчик данных еще не загружено значение из текущей ячейки данных. Производим операцию LOAD из текущей ячейки памяти в счетчик данных. Выставляется флаг APLock

- Флаг стоит. Значит данные в счетчике уже загружены. Ничего не делаем

- Проверяем флаг APLock:

- Текущая инструкция < или >

- Проверяем флаг APLock

- Флаг снят. Ничего не делаем

- Флаг стоит. Производим операцию выгрузки текущего значения счетчика данных в ОЗУ. Снимаем флаг APLock

- Проверяем флаг APLock

- Текущая инструкция - другая

- Дополнительных действий не требуется.

- Исполняем текущую инструкцию

Каждая инструкция представлена в памяти 4-х разрядным значением, соответствующим тому или иному опкоду.

При этом, компьютер имеет дополнительные инструкции, которые предназначены для непосредственного управления машиной.

Для этого, в машине имеется 1-х разрядный регистр текущего набора команд. ISAREG, который в теории расширяет число инструкций до 32 - представляя два набора инструкций:

- ISAREG=0 - Debug ISA - режим, в котором машина находится после включения. в нем доступны инструкции очистки ОЗУ, сброса состояния машины, команды загрузки данных с перфоленты

- ISAREG=1 - Brainfuck ISA - основной режим, в котором доступны 8 инструкций языка brainfuck плюс несколько дополнительных

В реальности, одни и те же инструкции могут присутствовать в разных наборах. например инструкции выбора набора инструкций присутствуют везде, таким образом, в одном наборе может быть только до 14 инструкуций по существу.

Debug ISA (ISAREG=0)

| Символ | Опкод | Brainfuck | название | описание |

|---|---|---|---|---|

| N | 0x0 | NOP | No operation - Must be in both ISA set | |

| H | 0x1 | HALT | Must be in both ISA set | |

| 0x2 | ||||

| 0x3 | ||||

| 0x4 | ||||

| 0x5 | ||||

| { | 0x6 | LABEG | Если текущий адрес равен нулю - пропустить тело цикла | |

| } | 0x7 | LAEND | Если текущий адрес не равен нулю - выполнить итерацию цикла | |

| L | 0x8 | CLRL | Сбросить счетчик глубины вложенностей циклов | |

| I | 0x9 | CLRI | Сбросить счетчик инструкций | |

| 0 | 0xA | CLRD | Сбросить счетчик данных | |

| A | 0xB | CLRA | Сбросить счетчик адреса (Что делать с флагом захвата?) | |

| 0xC | ||||

| R | 0xD | RST | Hard reset | |

| D | 0xE | ISA2 | Set ISAREG=0 - Debug ISA | |

| B | 0xF | ISA3 | Set ISAREG=1 - Brainfuck ISA |

Загрузчик

загрузчик - код, который будет выполняться сразу после включения машины и подачи тактирования. Расположен по нулевому адресу в памяти. Bootloder is the code, which is performed after reset vector. In placed on the instruction address 0x00000;

Очистка памяти

После включения или перезагрузки, в ОЗУ данных может быть мусор. По правилам brainfuck - все ячейки должны изначально иметь нулевое состояние, в С такой код выглядит следующим образом:

for (i = 0; i < 30000; ++i)

{

Memory[i] = 0;

}

В формате инструкций компьютера DekatronPC, начальный код загрузчика выглядит так:

A0> //Установка счетчика адреса в нуль, Обнуление текущей ячейки данных и выбор следующей

{ // Пока текущее значение счетчика адреса не равно нулю:

0 >//Обнуление текущей ячейки данных и выбор следующей

}

B //Выбор Brainfuck ISA

PunchTape ISA (ISAREG=0) (в составе Debug ISA)

Предназначен для загрузки данных с перфоленты в память программ. Как именно это сделать - пока не понятно. Так как загрузчик использует счетчик инструкций и часть памяти программ для себя. Следовательно, необходимо реализовать возможность использования счетчика адреса в этих целях. Однако, счетчик адреса не в состоянии покрыть ведь диапазон памяти программ.

Второй вариант - использовать счетчик адреса загрузчиком. Но тогда не получится очистить память данных от мусора.

Третий вариант наиболее предпочтителен - использовать аппаратный способ загрузки - когда синхросигнал с перфоленты будет инкрементировать значение счетчика инструкций, а другой сигнал - подавать сигнал записи в память. Таким образом можно инструкцией запустить этот процесс и дальше аппаратные средства сделают все самостоятельно.

Brainfuck ISA (ISAREG=1)

Помимо восьми основных brainfuck-инструкций имеет еще 8 дополнительных. Особое внимание стоит уделить инструкциям CLRML, LOAD, STORE

Они могут быть использованы для копирования данных в памяти. счетчик данных может быть использован как временный регистр.

Допустим, нужно скопировать данные из ячейки А в ячейку Б.

- Счетчик адреса устанавливается на ячейку А

- Дается команда LOAD - данные загружаются из памяти в счетчик данных

- Стирается флаг памяти - CLRML. Возможно имеет смысл команду LOAD делать без поднятия флага, тогда эта операция будет не нужна

- Счетчик адреса устанавливается на ячейку Б

- Дается команда STORE. значение из счетчика данных выгружается в ячейку памяти Б

| Символ | Опкод | Brainfuck | название | описание |

|---|---|---|---|---|

| N | 0x0 | NOP | Пустая инструкция | |

| H | 0x1 | HALT | Останов машины | |

| + | 0x2 | + | INC | Increment of Current data cell |

| - | 0x3 | - | DEC | Decrement of current data cell |

| > | 0x4 | > | AINC | Increment of address pointer |

| < | 0x5 | < | ADEC | Decrement of address pointer |

| [ | 0x6 | [ | LBEG | If current data cell equal zero, skip the loop |

| ] | 0x7 | ] | LEND | If current data cell not equal zero, repeat loop iteration |

| . | 0x8 | . | COUT | Print current symbol to the terminal |

| , | 0x9 | , | CIN | Read symbol from the terminal (Blocked acces - Program halted while no symbol) |

| 0 | 0xA | [-] | CLRD | Basic brainfuck optimization: Write zero to current Data Cell |

| M | 0xB | CLRML | Clear memory lock | |

| G | 0xC | LOAD | Explicit Load from current memory cell to Data Counter | |

| S | 0xD | STORE | Explicit Store from Data Counter to current memory cell | |

| D | 0xE | ISA2 | Set ISAREG=0 - Debug ISA | |

| B | 0xF | ISA3 | Set ISAREG=1 - Brainfuck ISA |

Формат записи на магнитную ленту

Если использовать кассетный или бобинный магнитофон (типа ламповой коменты или яузы) для хранения программ и их последующего ввода в память машины, можно использовать DTMF-сигналы, когда двумя синусоидами кодируется до 16 символов. Так как программа пишется 4-х битовыми пачками, так что в одном сигнале сразу будет готовая инструкция. По завершении записи на ленте формируется прерывистый сигнал 0x01(HALT)

Декатронные счетчики

Декатронный счетчик представляет собой реверсивный многоразрядный счетчик на базе нескольких декатронов.

В ламповом компьютере требуется 4 таких счетчика с общим количеством декатронов в 17 штук.

Функционал счетчика:

- Инкремент и декремент текущего числа счетчика

- Для работы в режиме счета от 0 до 255 необходимо выставить TOP_LIMIT_MODE=1. Тогда по достижении счетчиком числа TOP_VALUE вместо инкремента будет происходить запись 0 в счетчик. По достижении 0 и при декременте - в счетчик будет записано TOP_VALUE.

- Запись числа в счетчик со входа In, заданного в формате 8-4-2-1

- Чтение числа из счетчика на выход Out, в формате 8-4-2-1

Все счетчики работают синхронно от сигнала тактирования и имеют следующие входы управления

- Dec - выбор направления счета - в прямую сторону (лог.0) и обратную сторону (лог.1)

- Count - при наличии этого сигнала по нарастающему фронту Clk совершается операция инкремента(Dec=0) и декремента(Dec=1) счетчика

- SetZero - при наличии этого сигнала по нарастающему фронту Clk совершается запись нуля в счетчик

- Set - при наличии этого сигнала по нарастающему фронту Clk производится запись числа со входа In в счетчика

| Платы | Триоды | Диоды |

|---|---|---|

| Схема чтения | 2 | 8 |

| Схема записи | 29 | 0 |

| Управление, перенос | 5 | 6 |

| Счетчик | Функционал | Чтение | Запись | Управление | Декатроны | Диоды | Триоды |

|---|---|---|---|---|---|---|---|

| IP Counter | Сброс в нуль, Чтение данных, Zero | 6 | 0 | 6 | 6 | 84 | 42 |

| AP Counter | Сброс в нуль, Чтение данных, Zero | 5 | 0 | 5 | 5 | 70 | 35 |

| Data Counter | Сброс в нуль, запись данных, чтение данных, Zero | 3 | 3 | 3 | 3 | 42 | 108 |

| Loop Counter | Сброс в нуль, Zero | 0 | 0 | 3 | 3 | 18 | 15 |

| Всего | 14 | 3 | 17 | 17 | 214 | 200 |

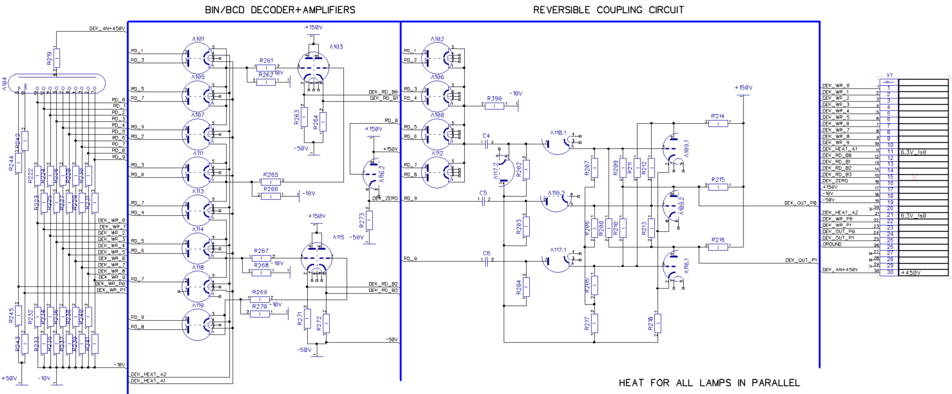

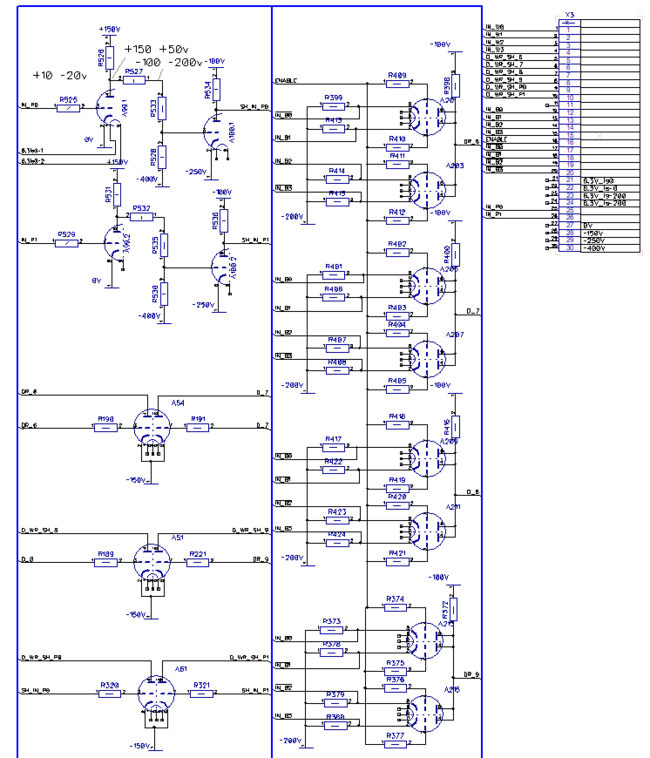

Экспериментальная декатронная ячейка

Ячейка представляет собой блок 3U-блок на 4 платы, и реализует полную схемотехнику управления декатроном, включая чтение, запись и пересчет с переносом.

Блок необходим для отладки схемотехники управления декатроном, особенно схемы записи числа в счетчик.

Основная плата - плата декатрона. На ней располагаются непосредственно сам декатрон, схема чтения, включающая в себя преобразователь двоичного-кода в двоично десятичный на диодах и катодные повторители-усилители. Отдельно идет катодный повторитель для сигнала нуля.

Также есть схема переноса. Технически это тройная защелка, имеющая два выхода, которые подсвечивают крайние положения - 0 и 9 до момента полного переключения лампы. т.е. этот блок помнит последнее состояние лампы пока идут процессы переключения.

Выход - 30-контактный. На нем есть все линии декатрона на запись, напряжения питания. накал, а также - двоично-десятичный выход 8-4-2-1

Еще две платы примерно одинаковые, их задача - преобразовать двоично-десятичный вход 8-4-2-1 в двоичный с сигналом записи - для этого требуется 4 инвертора, и 5-входовый И - на двух сдвоенных триодах, где анод-катод - это 4 линии и пятая линия - сетка.

К этим двум платам пока вопросы. На две платы следующие задачи:

- Инверторы входных сигналов 8-4-2-1. Итого имеем 8 сигналов - прямые и инверсные, которыми можем набрать нужную комбинацию сигналов для следующего этапа:

- Пятивходовые И на двух сдвоенных триодах, где сетка - это пятый сигнал записи. Им на вход подаются сигналы набранные в нужной комбинации на первом этапе.

- Усилители записи - 10 штук. По одному на каждый катод. И тут вопрос - либо они будут работать в статическом режиме, либо в импульсном. Первый вариант требует переход в отрицательные уровни напряжения. Второй позволяет обойтись без них, с помощью развязывающих конденсаторов формировать импульсы нужной длительности и амплитуды.

- Усилители сигналов управления подкатодами. тут опять вопрос к режиму работы. Скорее всего я приду к импульсному варианту - он проще и по нему есть все необходимые схемы.

Источники питания:

- ТСШ-170 - предназначен для выработки основного питания +150В, а также пары накальных линий для 6С19П. Трансформатор проверен на сопротивление изоляции.

- ТН61 - общей мощностью 190Вт. Имеет 4 линии 6.3В - 3 по 8А и 1 машина - 6.1А. Будет обеспечивать основное питание накалов ламп, разбитых на группы по смещениям.

- ТА48, мощностью 36Вт - питание декатрона +500В (технически сам источник будет на +350В), а также напряжение смещения -50В.

- ТА, мощностью 15Вт

Схемы питания берем из блоков питания осциллографов С1-54 и TR4401

Модули декатронного счетчика

Схема декатронного счетчика содержит две большие группы элементов- обязательная для любого из декатронов и необходимая схемотехнически.

Обязательной является:

- обвязка самого декатрона,

- усилители-формирователи управляющих испульсов, 1 лампа(?)

- трех-позиционная защелка схемы переноса 8 ламп(?)

- усилители-формирователи линии сброса в 0 и в Х (например в 5 для счетчика до 255), 1 лампа(?) - можно вынести на отдельную плату

Желательно уместить всю эту обвязку на одной плате.

Необходимая обвязка:

- Схема преобразователя позиционного кода в двоично-десятичный - 11 ламп

- Схема усилителей-формирователей позиционных линий для любого из катодов. Два усилителя находятся в обязательной секции, поэтому остается оп 8 линий на декатрон. Для счетчика данных требуется в общей сложности 17 линий. Можно округлить до 18 линий и разместить на 1-2 платах. Если в одну плату обязательная обвязка влезать не будет - то для счетчика данных требуется 23 линии, а для любого счетчика - от 6 до 10 линий. Исходя из этих данных нужно определиться с числом линий - однако нужно окончательно определиться со схемотехникой и определить требуемое количество ламп на одну линию.

- Схема декодера из двоично-десятичного в позиционный код. Требует по две лампы на линию. Вероятно собираться будет на базе элементов И.

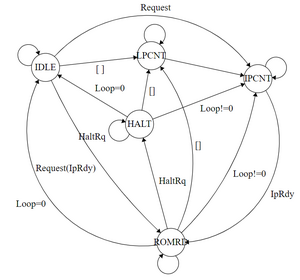

IpLine

Конечный автомат линии Ip Line объединяет в себе все основные стадии работы.

Так как блок состоит из двух счетчиков - IP Counter и Loop Counter, основной алгоритм работы конечного автомата - работа по внешнему кольцу состояний -

Готов -> Запрос нового адреса -> Запрос новой инструкции.

Однако, есть особые случаи:

- Сразу после сброса машины, на выходе счетчика уже находится адрес 0. Нужно сразу зачитывать инструкцию по этому адресу без инкремента счетчика.

- Если текущие инструкции - условные переходы [ ] и { } и условие перемотки инструкций выполняется - то одновременно поднимается CountRequest на оба счетчика.

- Если после выгрузки очередной инструкции оказывается:

- что значение LoopCounter == 0 - то перемотка завершена.

- что значение LoopCounter != 0 - то выдается новый IpCounteRequest сигнал

- что выставлен сигнал HaltRq - Система останавливается до снятия сигнала. в этом случае машина либо продолжит счет, либо перейдет в состояние IDLE

DekatronPC Challenge

Сейчас у меня собрано все железо, нужное для начала экспериментов, в том числе полторы тысячи сверхминиатюрных ламп - 6Н16Б, 6Х7Б и 6Ж2Б. Продолжается долгий и интересный процесс проектирования и сборки будущей машины. В отличие от релейного компьютера с его монолитной конструкцией, здесь конструкция блочная.

Этап 1: Верификационная программная модель C++ (UPD: 19.05.2023)

Создан программный эмулятор на языке C++. При этом поведение модели такое же как будет в железе - 4 счетчика - для верификации алгоритма исполнения программ на brainfuck только на счетчиках. Модель поддерживает только 8 базовых инструкций языка Brainfuck и требует доработки для дополнения остальными инструкциями. В итоге модель должна стать блоком для верификации дизайна на Verilog.

Завершением этапа будет программный код, поддерживающий расширенный набор инструкций описанный выше.

Этап 2: FPGA-Эмулятор лампового компьютера (UPD: 22.05.2023)

Архитектура машины реализуетсяна языке Verilog. А также изготавливается эмулятор лампового компьютера на базе ПЛИС. На данный момент модель уже умеет исполнять программу Hello World! Идет активная переработка исходного кода. Также, на базе Verilator создано окружение виртуального эмулятора - он позволяет отлаживать прошивку Эмулятора без физического доступа к железу, в виде C++ приложения, в котором код Эмулятора пишется на языке Verilog.

Тестирование:

| Тест | Состояние |

|---|---|

| Dekatron | PASSED |

| Counter | PASSED |

| IpLine - LoopTest | PASSED |

| Hello World | PASSED |

| Pi | FAILED |

В завершении этапа будет синтезируемый код на языке Verilog, работающий на FPGA-эмуляторе и позволяюющий запускать любые программы языка brainfuck

Этап 3: Экспериментальная декатронная ячейка (UPD: 19.05.2023)

Параллельно, ведется третий этап - изготовление экспериментальной декатронной ячейки, задача которой - отладка схемотехники управления декатроном - чтение, запись, счет.

Этап 4: Сборка в железе

На этом этапом будет последовательное создание блоков машины в железе и их подключение к Эмулятору. Получается, что блоки можно будет использовать для реальных вычислений по ходу строительства компьютера. Потом, замещая один за другим эмулируемые блоки реальным железом, мы полностью избавимся от ПЛИС, и ламповый компьютер станет полностью самостоятельным. Проект будет считаться завершенным, когда от ПЛИС в системе не останется и следа.

Часто-задаваемые вопросы и ответы

- Зачем?

- Затем.

- Почему brainfuck? Может быть лучше взять более практичный урезанный ассемблер?

- brainfuck - и есть урезанный ассемблер. Ламповая машина в любом случае будет в миллион раз медленнее современных компьютеров и проект является видом инженерного искусства. А раз так - то реализовывать надо наиболее безумный вариант. Тем более что декатрон - основа машины - позволяет реализовать brainfuck и ничего более.

- Питание?

- Каждый блок будет оснащен своим собственным источником накального напряжения. Основной источник накального - трансформаторы ТН60 и ТН61.

- Напряжения смещения а также напряжение питания декатронов - анодные трансформаторы ТА и ТПП подходящей мощности и напряжений. Все напряжения смещения будут оборудованы стабилизаторами выходного напряжения. Эти напряжения подаются через пускатель по команде общего блока управления - после прогрева ламп.

- Основное анодное напряжение - некоторые блоки будут получать от собственных силовых трансформаторов типа ТС160, ТС170, ТС270 - это трансформаторы от ламповых телевизоров. а также от трансформаторов типа ТА подходящей мощности. Стабилизаторов напряжения на выходе не будет предусмотрено. Анодное на схему будет подаваться через пускатель по команде общего блока управления после подачи накального напряжения и прогрева ламп, подачи напряжений смещения, анодного декатронов.

- Предусмотрен общий стабилизатор напряжения на базе автотрансформатора. От него будут питаться все остальные блоки.

Общий прогресс

Видеоматериалы

Ссылки

- Статья на Xakep.ru