Ламповая логика: различия между версиями

Материал из DekatronPC

Radiolok (обсуждение | вклад) Метка: визуальный редактор отключён |

Radiolok (обсуждение | вклад) |

||

| (не показана 1 промежуточная версия этого же участника) | |||

| Строка 1: | Строка 1: | ||

| Строка 4: | Строка 8: | ||

[[категория:Проекты]] | [[категория:Проекты]] | ||

Вариации схем для лампового компьютера | |||

{| class="wikitable" | {| class="wikitable" | ||

|+ | |+ | ||

| Строка 77: | Строка 81: | ||

| 1,9 | | 1,9 | ||

|Пассивная реализация. Будет работать только в составе прочих схем, например RS-защелок | |Пассивная реализация. Будет работать только в составе прочих схем, например RS-защелок | ||

|- | |||

| rowspan="2" |2-2AOI | |||

| | |||

|3 | |||

| | |||

|7,5 | |||

| rowspan="2" |And-Or_invert. ~(AB+CD). реализация может быть различной. Из аналогов кремниевого мира - два ИЛИ(пассивных?) и NAND. Реализации | |||

# на трех лампах элементах 6Н16Б | |||

# пассивные ИЛИ, активный НЕ | |||

|- | |||

| | |||

|1 | |||

|2 | |||

|5 | |||

|- | |- | ||

| rowspan="2" |2NAND | | rowspan="2" |2NAND | ||

| Строка 103: | Строка 122: | ||

|6,9 | |6,9 | ||

| rowspan="2" |Технически это RS-защелка, два элемента И, скорее всего пассивных, плюс инвертор. Последний может быть как на 6Ж2Б, так и на половине 6Н16Б. По накалу опять же разницы нет. | | rowspan="2" |Технически это RS-защелка, два элемента И, скорее всего пассивных, плюс инвертор. Последний может быть как на 6Ж2Б, так и на половине 6Н16Б. По накалу опять же разницы нет. | ||

|- | |- | ||

| - | | - | ||

| Строка 115: | Строка 133: | ||

| | | | ||

| | | | ||

| | |Предполагается, что D-триггер будет иметь аналогичную DLATCH схемотехнику, с конденсатором на линии C. Но это не точно. Также нужен сигнал для асинхронного сброса - потребуется доп. схема. | ||

|- | |- | ||

|DFFSR | |DFFSR | ||

| Строка 122: | Строка 140: | ||

| | | | ||

| | | | ||

| | |Триггер с синхронным сбросом | ||

|} | |} | ||

Текущая версия на 13:19, 2 октября 2023

Вариации схем для лампового компьютера

| Схема | 6Ж2Б | 6Н16Б | 6Х7Б | Накал на элемент[1], Вт | Примечание |

|---|---|---|---|---|---|

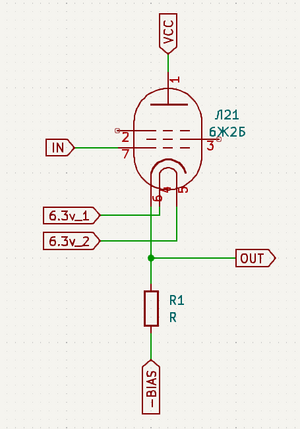

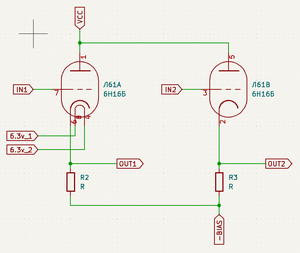

| BUF | 1 | - | - | 1.25 | Катодный повторитель Позволяет согласовать цепь с высоким сопротивлением с цепью с низким. Увеличивает нагрузочную способность линии. |

| - | 0,5 | - | |||

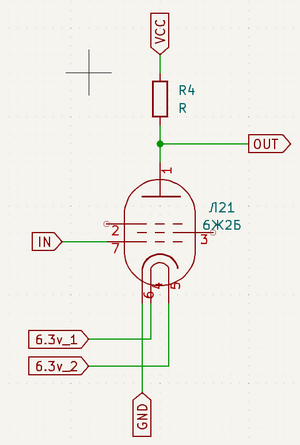

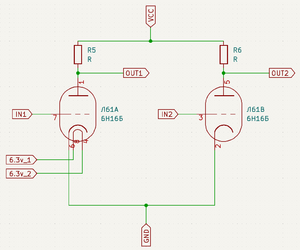

| NOT | 1 | - | - | 1,25 | Вероятно что для утилизации имеющегося количества 6Ж2Б часть плат инверторов будет собрана именно на этих лампах. |

| - | 0,5 | - | |||

| 2NOR | 2 | - | - | 2,5 | Предположительно, на разъеме платы можно будет осуществить внешнюю коммутацию и превратить два инвертора в один элемент 2ИЛИ-НЕ. |

| - | 1 | - | |||

| 2OR | - | 1 | - | 2,5 | Два буфера катодных повторителя. |

| - | - | 1 | 1,9 | Пассивный элемент,, Но не во всех цепочках его можно реализовать. | |

| 2AND | 1 | - | 1 | 3,15 | Элемент реализуется на сдвоенном диоде 6Х7Б работающий в комбинации с катодным повторителем. Может быть реализован как в паре 6Х7Б+6Ж2Б, так и 6Х7Б+6Н16Б. На два элемента потребуется в первом случае 4 лампы, во втором - три. По накалу - одинаково. |

| - | 0,5 | 1 | 3,15 | ||

| - | - | 1 | 1,9 | Пассивная реализация. Будет работать только в составе прочих схем, например RS-защелок | |

| 2-2AOI | 3 | 7,5 | And-Or_invert. ~(AB+CD). реализация может быть различной. Из аналогов кремниевого мира - два ИЛИ(пассивных?) и NAND. Реализации

| ||

| 1 | 2 | 5 | |||

| 2NAND | 1 | - | 1 | 3,15 | Элемент реализуется на сдвоенном диоде 6Х7Б работающий в комбинации с инвертором. Может быть реализован как в паре 6Х7Б+6Ж2Б, так и 6Х7Б+6Н16Б. На два элемента потребуется в первом случае 4 лампы, во втором - три. По накалу - одинаково. |

| - | 0,5 | 1 | 3,15 | ||

| RSLATCH | - | 1 | - | 2,5 | реализуется на одной лампе 6Н16Б. Возможно реализация на двух 6Ж2Б даст какие-то дополнительные возможности по сеткам. Но это требует исследования |

| DLATCH | 1 | 1 | 2 | 6,9 | Технически это RS-защелка, два элемента И, скорее всего пассивных, плюс инвертор. Последний может быть как на 6Ж2Б, так и на половине 6Н16Б. По накалу опять же разницы нет. |

| - | 1,5 | 2 | 6,9 | ||

| DFF | Предполагается, что D-триггер будет иметь аналогичную DLATCH схемотехнику, с конденсатором на линии C. Но это не точно. Также нужен сигнал для асинхронного сброса - потребуется доп. схема. | ||||

| DFFSR | Триггер с синхронным сбросом |

BUF

| Буфер на пентоде. Схема упрощенная | два буфера на сдвоенном триоде. Схема упрощенная |

INV

| инвертор на пентоде. Схема упрощенная | два инвертора на сдвоенном триоде. Схема упрощенная |

- ↑ Расчет мощности накала на логическую ячейку. Если число ламп нецелое число - то мощность накала на лампу также берется только частично